倾佳电子杨茜销售团队认知培训教程 碳化硅MOSFET应用在电力电子换流回路的分析:微观电场与宏观磁场的耦合研究

BASiC Semiconductor基本半导体一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 绪论:宽禁带半导体的物理范式转移

1.1 电力电子换流的演进与物理极限

电力电子技术的核心在于电能的高效变换与控制,而其基础单元——功率半导体开关器件,始终是制约系统性能的瓶颈。在过去的数十年中,硅(Silicon, Si)基器件如IGBT(绝缘栅双极型晶体管)和MOSFET(金属-氧化物半导体场效应晶体管)主导了该领域。然而,硅材料本身的物理属性决定了其性能极限。硅的禁带宽度仅为1.12 eV,临界击穿电场约为0.3 MV/cm,这导致高压硅器件必须采用较厚的漂移层来维持阻断电压,从而大幅增加了导通电阻(Ron)。为了降低导通损耗,IGBT引入了电导调制效应,利用少数载流子(空穴)注入来降低漂移区电阻,但这不可避免地带来了关断时的“拖尾电流”现象,限制了开关频率的提升并增加了开关损耗。

碳化硅(Silicon Carbide, SiC),特别是4H-SiC晶型,代表了一场物理范式的转移。其禁带宽度高达3.26 eV,临界击穿电场约为硅的10倍(~3 MV/cm),热导率更是硅的3倍(~4.9 W/cm·K)。这些本征物理优势使得SiC MOSFET能够在维持高耐压的同时,采用极薄的漂移层和更高的掺杂浓度,从而实现极低的比导通电阻(Ron,sp)。更关键的是,作为单极型器件,SiC MOSFET没有少数载流子存储效应,理论上可以实现极高的开关速度(dv/dt>100V/ns, di/dt>5A/ns)。

1.2 换流回路中的场耦合挑战

然而,SiC MOSFET的优异性能并非“免费午餐”。当我们将这些超高速器件置入实际的电力电子换流回路(Commutation Loop)中时,传统的电路分析方法已不足以描述其行为。极高的电压和电流变化率(slew rates)激活了电路中的寄生参数,导致微观层面的半导体内部电场与宏观层面的回路磁场发生复杂的相互作用。

换流回路通常定义为包含直流母线电容、高侧开关、低侧开关以及互连母排的最小电流路径。在SiC时代,这个回路不再仅仅是电流的通道,而是一个储能与辐射系统。微观上,器件内部耗尽层的快速扩展与收缩产生巨大的位移电流;宏观上,回路中的寄生电感在di/dt冲击下产生强磁场,导致电压过冲和振荡。这种电场与磁场的动态耦合,直接决定了系统的效率、可靠性(EMI/EMC)以及器件的寿命。

倾佳电子杨茜从物理本质出发,剖析SiC MOSFET在换流回路中的行为。我们将不再局限于集总参数电路模型,而是结合微观电场分布(载流子动力学、耗尽层演变)与宏观磁场分布(集肤效应、邻近效应、磁场抵消),对SiC MOSFET的开关瞬态进行多维度的解构分析。同时,结合基本半导体(BASiC Semiconductor)的最新工业级与车规级模块技术参数,探讨先进封装与驱动技术如何应对这些物理挑战。

2. SiC MOSFET微观物理机制与电场动力学

2.1 晶体结构与载流子输运特性

SiC材料的优越性根植于其晶体结构。Si-C键的键能远高于Si-Si键,赋予了材料极高的化学稳定性和机械强度,同时也带来了更宽的禁带宽度。在4H-SiC中,电子在晶格中的运动受到各向异性的影响,但其饱和漂移速度(2×107cm/s)是硅的2倍。这意味着在高电场下,载流子能以更快的速度穿过耗尽区,有助于缩短开关时间。

对于高压功率器件,导通电阻主要由漂移区电阻Rdrift决定。根据Baliga优值(BFOM),理想的漂移区比导通电阻与击穿电压(BV)的关系为:

Ron,sp=ϵsμnEc34(BV)2

其中ϵs是介电常数,μn是电子迁移率,Ec是临界击穿电场。由于Ec出现在分母的立方项,SiC材料10倍于Si的临界电场意味着在理论上,Ron,sp可以降低约3个数量级(~1000倍)。这种物理特性允许设计者在1200V甚至更高电压等级下使用单极型的MOSFET结构,而无需诉诸于双极型的IGBT结构4。

2.2 静态阻断下的微观电场分布

当SiC MOSFET处于关断状态(Blocking State)时,其承受着高直流母线电压(例如800V或1000V)。此时,器件内部的P-body与N-drift形成的PN结处于反偏状态。由于N-drift区的掺杂浓度远低于P-body区,耗尽层主要向漂移区深处扩展。

在微观尺度上,电场分布并非均匀。在平面栅(Planar Gate)结构中,P-well的曲率处会出现电场集中效应;在沟槽栅(Trench Gate)结构中,沟槽底部的氧化层拐角处是电场应力最集中的区域。SiC的高临界电场是一把双刃剑:虽然半导体本身能承受3 MV/cm的场强,但栅极氧化层(SiO2)的长期可靠性极限通常在3-4 MV/cm左右。如果漂移区的高电场耦合进氧化层,将导致栅氧击穿或经时击穿(TDDB)。

因此,现代SiC MOSFET(如BASiC的第三代芯片技术)通常采用复杂的屏蔽结构,如在沟槽底部注入P+屏蔽层(P-shield),将高峰电场限制在SiC体内,从而保护脆弱的栅氧化层。这种结构设计直接影响了器件的寄生电容,特别是栅-漏电容Cgd(即Crss)的大小和非线性特性7。

2.3 开关瞬态中的耗尽层动力学与位移电流

SiC MOSFET的开关过程,本质上是内部耗尽层电荷的建立与消散过程。这一过程伴随着剧烈的微观电场变化。

2.3.1 关断过程(Turn-off)

当栅极电压VGS下降至米勒平台电压以下,沟道关闭,电子电流切断。此时,外部负载电流强制维持不变(对于感性负载),迫使漏源电压VDS迅速上升。

在微观层面,随着VDS的升高,P-body/N-drift结的反偏电压增加,耗尽层迅速向N-drift区扩展。这一过程中,N型区中的多数载流子(电子)被抽离,留下了带正电的施主离子(空间电荷)。这个物理过程等效于对输出电容Coss进行充电。

关键在于,电场的快速变化(∂E/∂t)根据麦克斯韦方程组,会产生位移电流密度Jdisp:

Jdisp=ϵs∂t∂E

这个位移电流在宏观上表现为流经Coss(特别是Cgd和Cds)的电流。由于SiC器件能够承受极高的dv/dt(例如50-100 V/ns),由此产生的内部位移电流密度极大。这部分电流并不经过沟道,而是直接穿过耗尽区,成为关断损耗和电磁干扰(EMI)的重要源头。

2.3.2 动态雪崩(Dynamic Avalanche)

在极端快速的关断过程中,如果dv/dt过高,耗尽层内的载流子可能获得足够的动能引发碰撞电离,即使宏观电压尚未达到静态击穿电压。这种现象称为动态雪崩。虽然SiC材料具有较高的雪崩耐受性,但频繁的动态雪崩会导致局部热点,通过热-电反馈机制影响器件的长期可靠性。TCAD仿真显示,在某些条件下,关断时的电场峰值可能会瞬间超过临界值,导致空穴电流注入P-well,这在宏观上表现为关断电流的拖尾或振荡。

3. 换流回路的宏观磁场分析与寄生电感

3.1 换流回路的物理定义与磁能存储

电力电子换流回路是能量交换的核心舞台。在典型的半桥拓扑中,换流回路包括:

直流支撑电容(DC-Link Capacitor)。

正负极连接母排(Busbar)。

上桥臂开关器件(High-Side Switch)。

下桥臂开关器件(Low-Side Switch)。

根据安培环路定理,任何载流导体周围都会产生磁场。换流回路包围的面积内穿过的磁通量Φ与回路电流I的比值定义了回路的寄生电感Lloop:

Lloop=IΦ=I∬SB⋅dS

系统的磁场能量存储为Em=21LloopI2。在SiC应用中,由于开关速度极快,电流的变化率di/dt非常大。例如,BASiC BMF540R12MZA3模块在双脉冲测试中,关断di/dt可达11.89 kA/μs(即11.89 A/ns)。这意味着哪怕极小的寄生电感也会产生巨大的感应电动势。

3.2 寄生电感的物理构成与影响

寄生电感并非单一元件,而是分布在整个物理结构中:

电容ESL:电容器内部结构产生的等效串联电感。

母排杂散电感:连接电容与模块端子的导体产生的电感。

模块内部电感:包括功率端子、键合线(Bond wires)、DBC铜层路径等产生的电感。

根据法拉第电磁感应定律,在关断瞬间,回路中的寄生电感会感应出一个反向电压来阻碍电流的减小:

Vovershoot=Lloop×dtdi

假设回路总电感为30 nH(这是BMF240R12KHB3模块测试条件下的典型值9),在10 A/ns的关断速度下,产生的电压过冲高达300V。如果直流母线电压为800V,器件两端将承受1100V的电压,逼近1200V的额定击穿电压。这不仅压缩了安全裕度,还会在寄生电容和电感之间引发高频LC振荡(Ringing),向外辐射严重的电磁干扰。

3.3 高频下的磁场效应:集肤与邻近效应

在SiC的高频开关(几十kHz至MHz)和谐波分量下,导体的电流分布不再均匀。

集肤效应(Skin Effect) :高频电流倾向于流向导体表面,导致电流密度分布不均,有效截面积减小,交流电阻增加。这虽然对电感影响较小,但显著增加了热损耗。

邻近效应(Proximity Effect) :在换流回路中,正极母排和负极母排通常紧挨着布置。当流过相反方向的电流时,它们产生的磁场在导体之间的区域相互叠加增强,而在导体外部相互抵消。这种磁场分布会“挤压”电流流向两个导体的内侧表面。

**磁场抵消(Magnetic Field Cancellation)**是低电感设计的核心物理原理。通过叠层母排(Laminated Busbar)或模块内部的叠层DBC设计,使得流出电流和回流电流的路径尽可能重合且方向相反,可以最大限度地抵消外部磁场。根据能量定义L=2Em/I2,磁场能量Em的减少直接意味着寄生电感的降低。

BASiC Semiconductor的Pcore™2模块技术采用了这种低电感设计理念。例如,其内部布局优化了键合线和DBC铜层的走向,利用互感效应(Mutual Inductance)来降低总回路电感。在BMF540R12MZA3模块中,通过优化端子布局和内部互连,实现了适应高频开关的低杂散电感特性。

4. 米勒效应与位移电流路径的本质剖析

4.1 米勒电容的物理本源

SiC MOSFET的栅极与漏极之间存在寄生电容Cgd,又称米勒电容(Crss)。从微观结构上看,它主要由两部分组成:

栅-漏重叠电容:栅极多晶硅与N-drift区在JFET区域的物理重叠。

耗尽层电容:随着VDS增加,漂移区耗尽层扩展,相当于增加了电容器极板间距,导致Cgd随电压升高而急剧减小。

在BASiC BMF540R12MZA3模块中,25°C、800V时,Crss典型值仅为0.07 nF(70 pF),而输入电容Ciss为33.6 nF。这种巨大的比值差异是SiC器件的一个显著特征,也是其高速开关的物理基础。然而,在低电压(VDS较小)时,Crss会显著增大,这在开关瞬态的起始阶段尤为关键。

4.2 位移电流路径与串扰(Crosstalk)

在桥式电路中,当一个开关管(例如上管)快速开通时,桥臂中点电压VDS,low会以极高的dv/dt上升。对于处于关断状态的下管,这个dv/dt施加在其Cgd上,产生位移电流IMiller:

IMiller=Cgd⋅dtdvDS

这个电流必须寻找回路流回源极。其主要路径是:从漏极通过Cgd进入栅极节点,再经过栅极电阻RG(包括内部电阻Rg(int)和外部电阻Rg(ext))流向驱动器的负压源,最后回到源极。

根据欧姆定律,这个电流在栅极回路总电阻上产生压降:

VGS,induced=VEE+IMiller⋅(Rg(int)+Rg(ext))

如果这个感应电压VGS,induced超过了SiC MOSFET的阈值电压VGS(th),下管将发生误导通(Parasitic Turn-on) 。由于SiC MOSFET的阈值电压通常较低(BMF540R12MZA3典型值为2.7V,高温下更低),且能够承受的dv/dt极高,这种风险远高于硅基IGBT。

4.3 驱动方案中的物理对策:米勒钳位

为了对抗上述物理机制,BASiC Semiconductor在驱动方案中建议使用**米勒钳位(Miller Clamp)**功能。

物理机制:米勒钳位电路在检测到栅极电压低于一定阈值(表明器件已关断)时,通过一个低阻抗的MOSFET将栅极直接短路到负母线(或源极)。

场效应分析:这实际上是在栅极节点创造了一个极低阻抗的分流路径。位移电流IMiller不再流经较大的外部电阻Rg(ext),而是通过钳位管旁路。这使得栅极节点的电势被“钉”在低电平,防止电场在栅氧化层处建立足以开启沟道的电势势垒。

数据支撑:文档中的双脉冲测试对比显示,在无米勒钳位时,下管VGS尖峰可达7.3V(超过阈值),而启用钳位后尖峰被压制在2V以内,有效避免了直通风险。

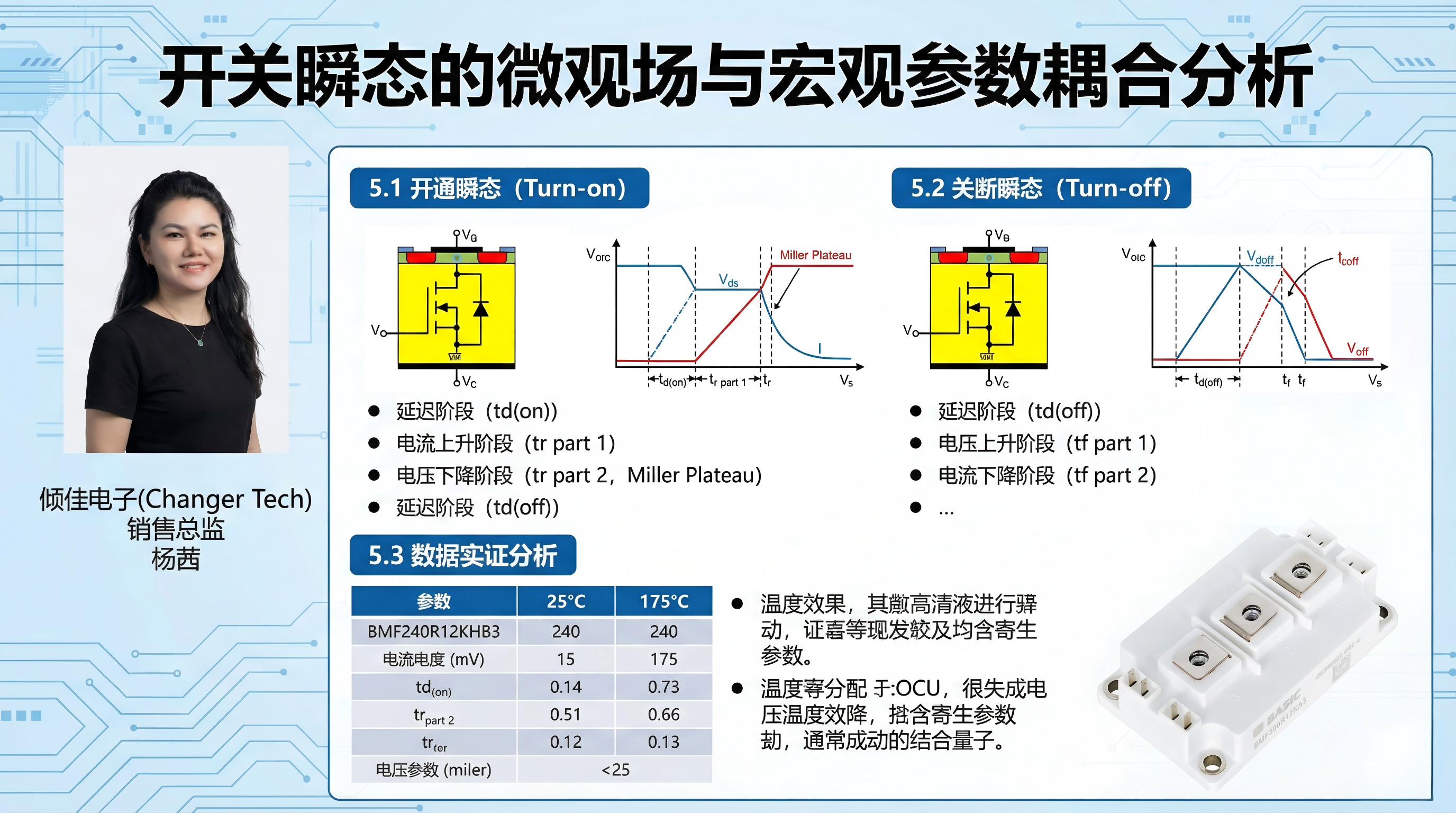

5. 开关瞬态的微观场与宏观参数耦合分析

5.1 开通瞬态(Turn-on)

延迟阶段(td(on)) :驱动电流对Cgs充电,栅极电场建立,直到VGS达到Vth。此时无主电流流通。

电流上升阶段(tr part 1) :沟道开启,电子在横向电场作用下从源极注入沟道,进入漂移区。漏极电流ID迅速上升。此时,di/dt最大,回路寄生电感Lσ感应出负电压(Vdrop=Lσ⋅di/dt),使得芯片实际承受的VDS下降。

电压下降阶段(tr part 2, Miller Plateau) :当ID达到负载电流后,VDS开始下降。此时漂移区的耗尽层迅速收缩,电场能量释放。这一过程产生巨大的位移电流流经Cgd,抵消了栅极驱动电流,形成米勒平台。SiC器件由于漂移层薄,这一阶段极快。

5.2 关断瞬态(Turn-off)

延迟阶段(td(off)) :Ciss放电,VGS降至米勒平台电压。

电压上升阶段(tf part 1) :沟道逐渐夹断。漂移区耗尽层迅速扩展,以承受不断上升的VDS。这一阶段是微观电场变化最剧烈的时期。高dv/dt不仅产生米勒电流,还可能在特定区域引发动态雪崩。

电流下降阶段(tf part 2) :VDS升至母线电压以上(由于杂散电感引起的过冲)。电流迅速下降,di/dt为负。寄生电感产生正向感应电动势Vovershoot=Lσ⋅∣di/dt∣,叠加在母线电压上,对器件的阻断能力构成挑战。

5.3 数据实证分析

以BMF240R12KHB3模块为例,其规格书给出的测试条件下,关断延迟时间td(off)为110ns,下降时间tf为36ns(25°C)。但在175°C下,td(off)增加到124ns,而tf略微增加至39ns。

温度效应的物理根源:高温下,SiC MOSFET的阈值电压降低,导致关断延迟增加(需要放电到更低的电位)。同时,MOSFET通道电阻增加,但由于开关速度主要受寄生电容和驱动能力限制,tf的变化相对较小。然而,内部栅极电阻Rg(int)随温度略有上升(2.47Ω -> 2.51Ω ),略微减慢了栅极放电速度。

寄生参数的影响:测试条件中标注使用了30nH的杂散电感。这个电感值在高速关断(例如几千安培每微秒)时,将产生数十伏甚至上百伏的电压尖峰。

6. 模块封装技术的电磁场优化

6.1 低电感封装设计的物理逻辑

为了应对SiC的高速开关特性,BASiC Semiconductor的Pcore™2系列模块采用了低电感设计。其物理本质是通过减小电流回路包围的面积来降低磁通量。

叠层母排结构:在模块内部,DC+和DC-端子及铜层通常设计为平行且紧邻的结构。根据安培定律,反向电流产生的磁场在空间中相互抵消。磁场能量密度wm=B2/2μ在两导体外部急剧下降,从而大幅降低了等效电感。

开尔文源极(Kelvin Source) :在BMF540R12MZA3等模块中,驱动回路的源极连接与功率回路的源极连接在物理上是分离的。

物理意义:功率回路的源极引线电感LS,power上存在巨大的L⋅di/dt压降。如果是共源极设计,这个压降会直接反馈到栅极回路,削弱驱动电压(负反馈),减缓开关速度并增加损耗。开尔文连接在微观电路上切断了这一公共阻抗耦合,使得栅极驱动仅“看到”芯片本身的源极电位,从而充分释放SiC的开关潜能。

6.2 绝缘材料的电场管理

SiC器件不仅电压高,而且允许更高的结温(175°C)。BASiC模块采用了**Si3N4 AMB**(活性金属钎焊氮化硅)陶瓷基板。

热-机-电耦合:Si3N4不仅具有优良的导热性(~90 W/mK),更重要的是其断裂韧性极高,能承受SiC芯片在高温循环下产生的巨大热应力。

电场强度:AMB工艺允许更厚的铜层,这不仅增加了热容,还通过优化铜层边缘的刻蚀形状(如阶梯状或圆角),缓解了陶瓷/铜界面处的三结合点(Triple Point)电场集中,防止在高压下的局部放电(Partial Discharge)。

7. 结论

SiC MOSFET在电力电子换流回路中的应用,不仅仅是器件的替换,而是一场涉及微观半导体物理与宏观电磁场的系统工程。

微观电场层面:SiC的宽禁带特性允许极高的临界电场,从而实现了低阻抗的漂移区。但这也导致了开关过程中耗尽层内极高的位移电流密度。米勒效应不再仅仅是参数上的电容耦合,而是高能电场动态演变的直接体现。理解这一点,对于设计能够有效抑制串扰的驱动电路至关重要。

宏观磁场层面:高di/dt使得极其微小的寄生电感(nH级)都成为产生破坏性过压的元凶。换流回路的设计必须遵循磁场抵消原则。BASiC模块通过低电感封装和开尔文源极设计,从物理结构上抑制了磁场能量的有害积聚。

耦合效应:微观的极快开关速度激发了宏观的寄生场,而宏观的寄生场(如源极电感电压)又反过来通过负反馈影响微观的沟道控制。这种强耦合要求工程师在设计时必须具备“场”的视角。

综上所述,充分挖掘SiC MOSFET潜力的关键,在于对换流回路中微观电荷动力学与宏观电磁场分布的精确管控。通过先进的封装技术最小化寄生参数,配合智能的驱动策略管理动态电场,才能真正实现高频、高效、高可靠性的电力电子系统。

附录:关键参数表 (基于BASiC模块数据)

| 参数 | 符号 | BMF540R12MZA3 (典型值) | BMF240R12KHB3 (典型值) | 单位 | 测试条件 |

|---|---|---|---|---|---|

| 内部栅极电阻 | RG(int) | 1.95 | 2.85 | Ω | f=1MHz |

| 输入电容 | Ciss | 33.6 | 15.4 | nF | VDS=800V |

| 输出电容 | Coss | 1.26 | 0.63 | nF | VDS=800V |

| 反向传输电容 | Crss | 0.07 | 0.04 | nF | VDS=800V |

| 总栅极电荷 | Qg | 1320 | 672 | nC | - |

| 测试杂散电感 | Lσ | N/A | 30 | nH | 关断测试条件 |

| 开通延迟 | td(on) | - | 65 | ns | 25∘C |

| 关断延迟 | td(off) | - | 110 | ns | 25∘C |

| 开通损耗 | Eon | - | 11.8 | mJ | 25∘C |

| 关断损耗 | Eoff | - | 2.8 | mJ | 25∘C |

审核编辑 黄宇